by bitwiseblog.com | Apr 18, 2026 | Blog, Systemverilog, UVM

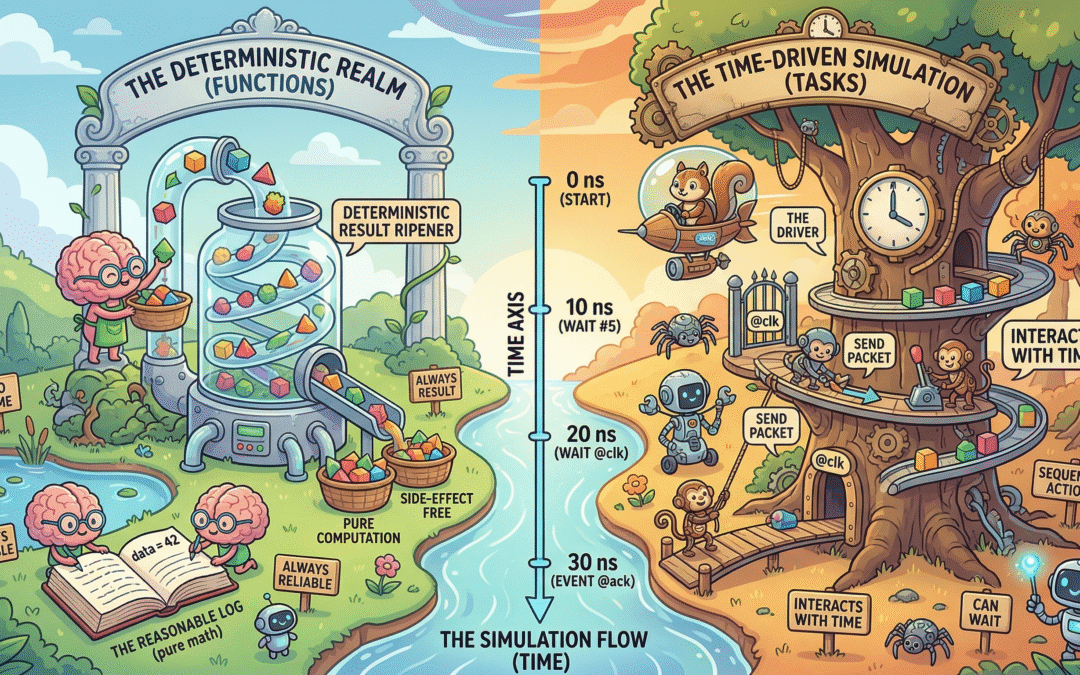

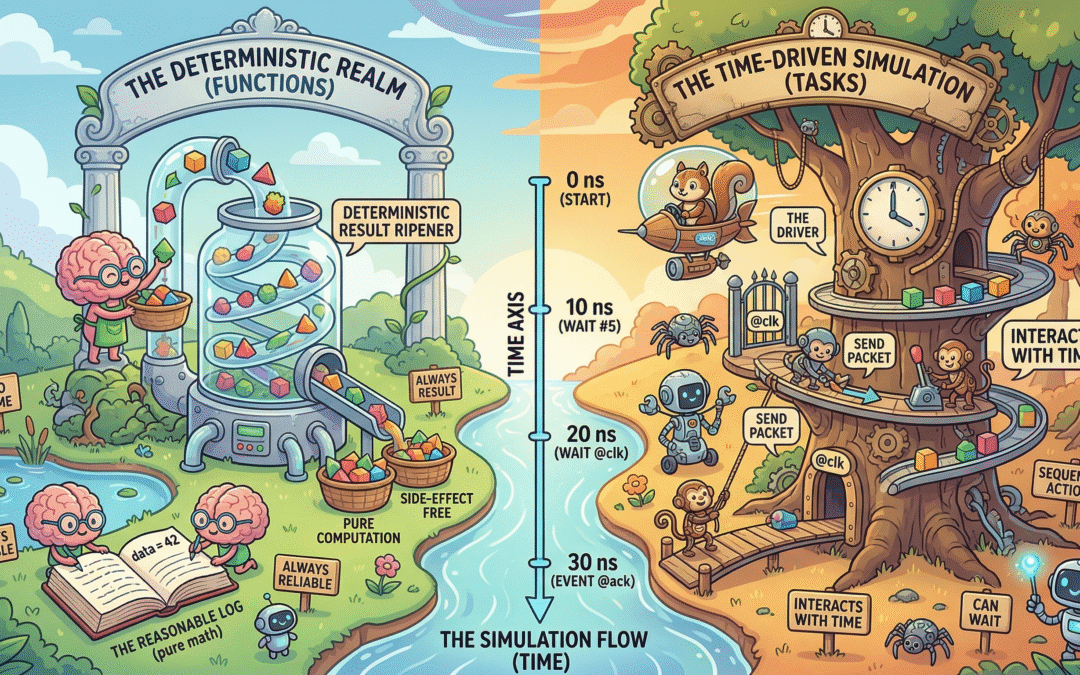

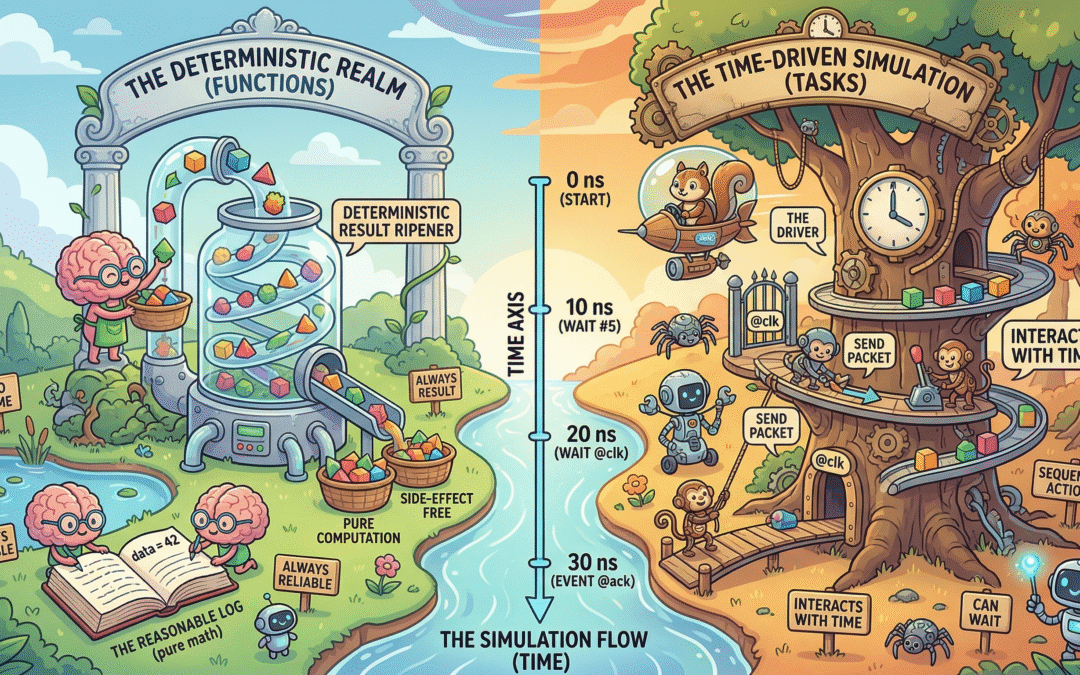

Stop Memorizing Syntax. Start Modeling Intent. When it comes to understanding SystemVerilog functions vs tasks, most engineers start with a quick checklist: functions return a value, tasks can consume time. That description is accurate, but it stops right where things...

by Anup Reddy | Nov 15, 2025 | Blog, Systemverilog

In SystemVerilog, macros provide a way to define reusable piece of code that can be inserted anywhere in your source code. SystemVerilog macros are very similar to c language macros. Macros essentially substitutes a name with a piece of code. From my early days with...

by Anup Reddy | Jan 20, 2024 | Blog, Systemverilog

Introduction We all know the importance of Transaction Level Modelling also known as TLM in UVM. The fundamental goal of TLM is to provide communication between components in a flexible, scalable and yet modular manner. Indeed, TLM does delivers on its promises. Every...