by Anup Reddy | Feb 15, 2026 | Blog, UVM

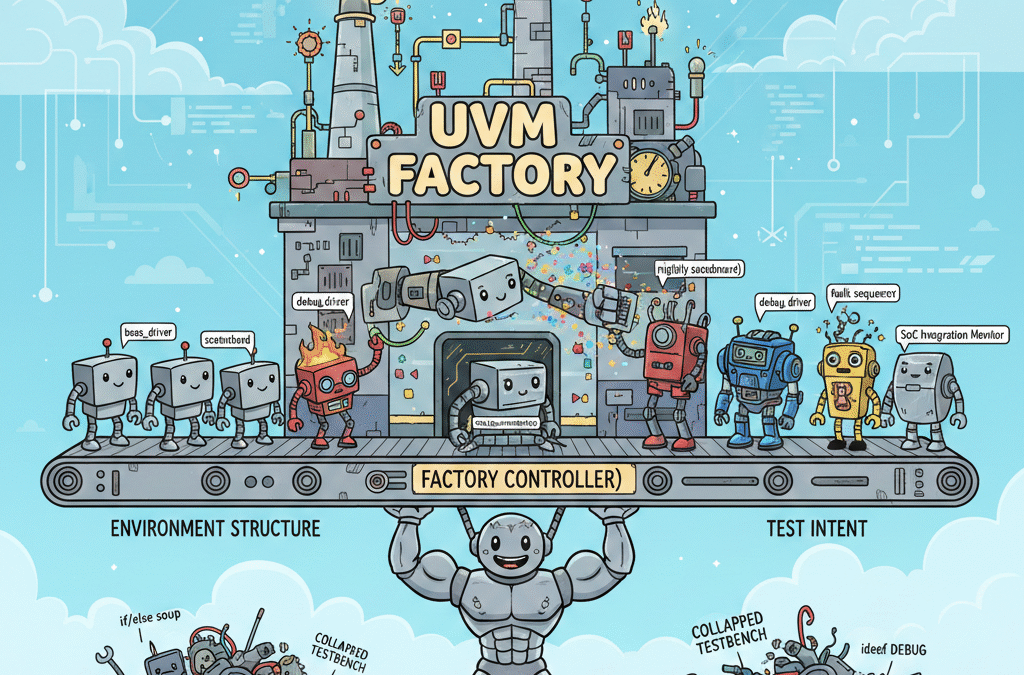

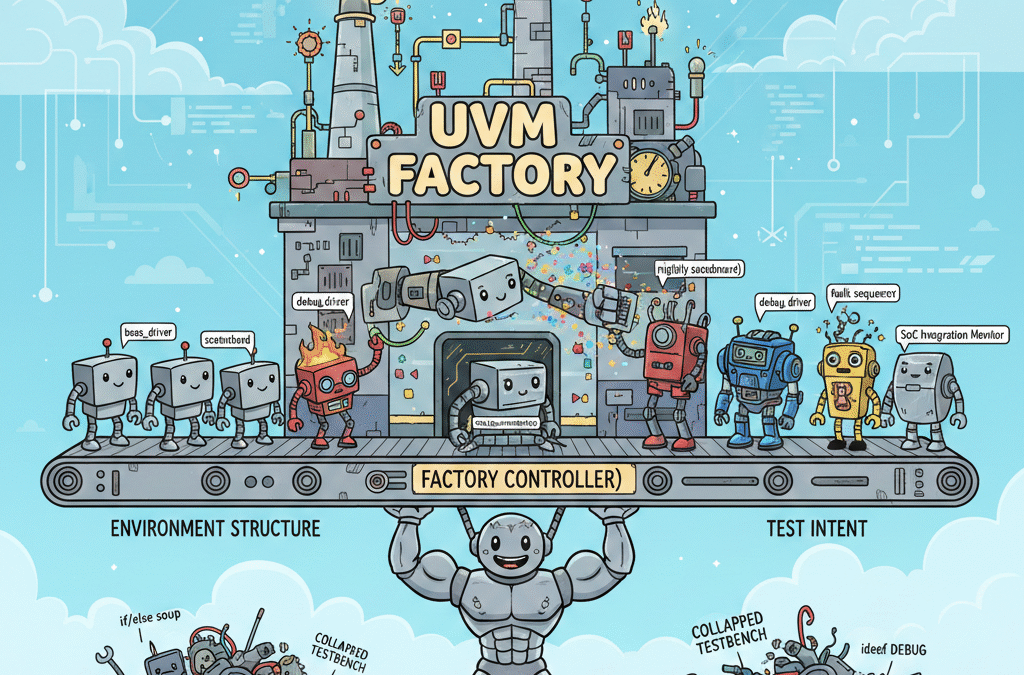

What You Actually Use Every Day If you read most explanations of the UVM factory, they begin with APIs. They explain set_type_override_by_type(), show a minimal example, and stop there. What’s missing is the architectural context: Why experienced verification...

by Anup Reddy | Nov 29, 2025 | Blog, UVM

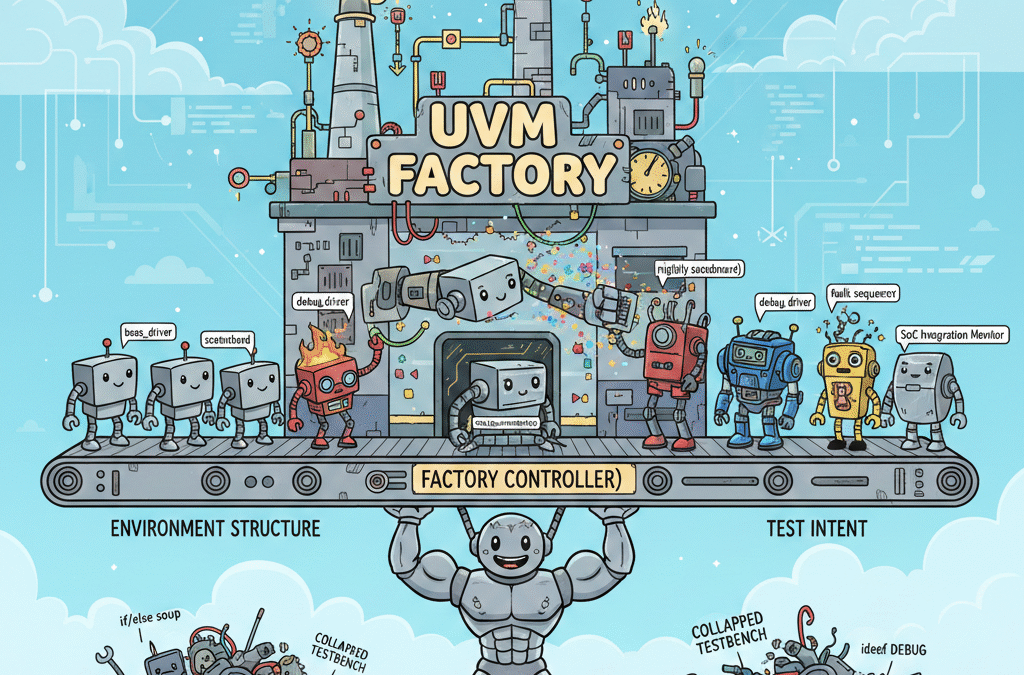

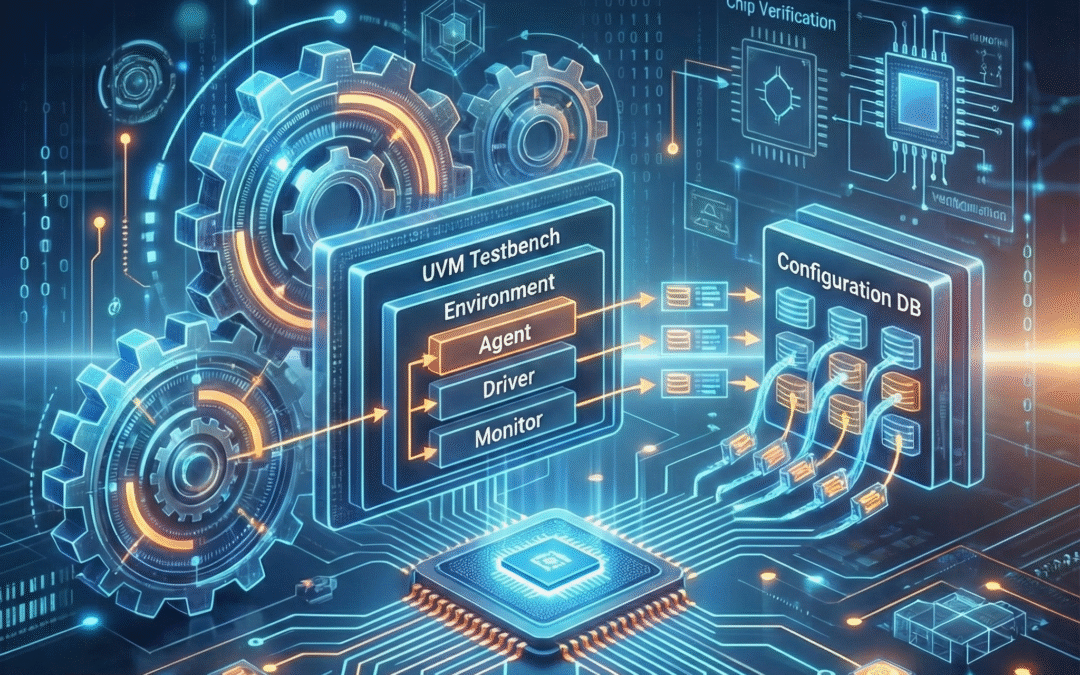

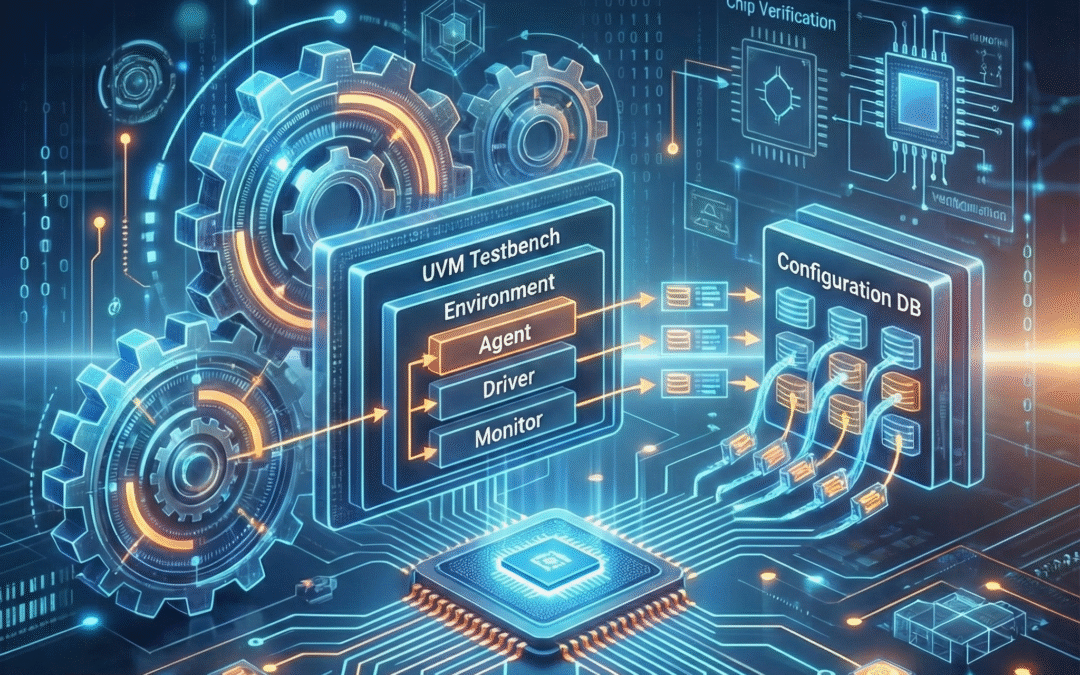

Introduction As UVM testbenches evolve from simple setups to complex, multi-layered environments, configuration management becomes one of the most critical and confusing aspects of maintaining control and flexibility. Every testbench you build, regardless of its...

by Anup Reddy | Nov 15, 2025 | Blog, Systemverilog

In SystemVerilog, macros provide a way to define reusable piece of code that can be inserted anywhere in your source code. SystemVerilog macros are very similar to c language macros. Macros essentially substitutes a name with a piece of code. From my early days with...

by Anup Reddy | Mar 2, 2024 | Systemverilog, UVM

Introduction In ASIC verification, we all use a method known as Metric Driven Verification but we don’t use that term much. Instead we always refer to it as Coverage Driven Verification. Although, both the terms means the same thing to some extent. There are...

by Anup Reddy | Jan 20, 2024 | Blog, Systemverilog

Introduction We all know the importance of Transaction Level Modelling also known as TLM in UVM. The fundamental goal of TLM is to provide communication between components in a flexible, scalable and yet modular manner. Indeed, TLM does delivers on its promises. Every...